#### Comments of the Semiconductor Industry Association (SIA) To the Internal Revenue Service On the Advanced Manufacturing Investment Credit, Notice of Proposed Rulemaking REG-120653-22 88 Fed. Reg. 17451 (March 23, 2023)

#### May 22, 2023

The Semiconductor Industry Association (SIA)<sup>1</sup> appreciates the opportunity to provide comments on the Internal Revenue Service (IRS) and Treasury Department (Treasury) notice of proposed rulemaking<sup>2</sup> ("Proposed Regulations") related to the Advanced Manufacturing Investment Credit enacted in the CHIPS and Science Act of 2022 ("CHIPS Act" or "the Act")<sup>3</sup> and set forth in section 48D of the Internal Revenue Code.<sup>4</sup>

The complex, technologically advanced process of designing and manufacturing semiconductors and semiconductor manufacturing equipment requires high levels of investment in people, facilities, and equipment due to the complexity of the technology and the rigorous and exacting standards needed for construction, equipment, and infrastructure. In light of the critical role of semiconductors to the U.S. economy and national security, Congress enacted the CHIPS Act to provide robust incentives for the expansion of the semiconductor ecosystem in the United States in order to make the U.S. competitive with other countries. These incentives consisted of two separate but complementary programs: (1) a program of direct manufacturing incentives under the authority of the Department of Commerce and (2) an "advanced manufacturing investment credit" codified under section 48D.

SIA commends the Treasury Department in adopting a holistic approach to section 48D in the Proposed Regulations so as to provide taxpayers with a credit for a wide range of investments necessary to manufacture semiconductors and semiconductor manufacturing equipment. We provide the following comments on the proposed rules and, as necessary, recommend clarifications to provide taxpayers with certainty in determining their eligibility to claim the credit. SIA also includes in Appendix A a "Brief Overview of Semiconductor Manufacturing and Equipment Manufacturing" to provide Treasury with additional information in support of our comments.

<sup>&</sup>lt;sup>1</sup> The Semiconductor Industry Association (SIA) is the voice of the semiconductor industry, one of America's top export industries and a key driver of America's economic strength, national security, and global competitiveness. SIA represents 99% of the U.S. semiconductor industry by revenue and nearly two-thirds of non-U.S. chip firms. Through this coalition, SIA seeks to strengthen leadership of semiconductor manufacturing, design, and research by working with Congress, the Administration, and key industry stakeholders around the world to encourage policies that fuel innovation, propel business, and drive international competition. Learn more at <a href="https://www.semiconductors.org">www.semiconductors.org</a>. <sup>2</sup> Advanced Manufacturing Investment Credit, Internal Revenue Service, Treasury, 88 Fed. Reg. 17451 (proposed

March 23, 2023) (to be codified at 26 CFR 1)

<sup>&</sup>lt;sup>3</sup> Pub. L. No.117-167 (2022).

<sup>&</sup>lt;sup>4</sup> All "section" or "§" references are to the Internal Revenue Code of 1986, as amended, and the regulations promulgated thereunder.

# I. Definitions. (§ 1.48D-2)

A. "Semiconductor"

In response to Treasury's request that taxpayers provide comments regarding the proposed definition of "semiconductor," SIA respectfully requests the term be modified so as to include mono or polycrystalline solid substances—such as polysilicon, ingot/boules, wafers, and similar materials—with electronic properties manufactured specifically for the purpose of semiconductor manufacturing (§ 1.48D-2(k)). Generally, Treasury should provide a more expansive definition of "semiconductor" to include a substance, system, or device because the production of semiconductor snecessarily requires the production of semiconductor grade polysilicon, semiconductor silicon wafers, compound semiconductors, such as silicon carbide and gallium nitride, or other types of boules, the singulation of the boules into individual wafers, the polishing of the wafers, and frequently the deposition of epi layers on the wafer. These highly complex manufacturing processes are integral to the semiconductor device. Put another way, polysilicon and similar materials are the "semiconductor" material in the semiconductor chip. The crystal structure of the boule or wafer forms the base of the finished wafer, which is manipulated through successive depositions, implants, etching, and other steps to create the chip.

The inclusion of polysilicon, boules, wafers and similar materials with electronic properties manufactured specifically for the purpose of semiconductor manufacturing would be consistent with existing Treasury guidance pertaining to the tax credit for the manufacture of solar panels. Specifically, with respect to the section 48C clean energy manufacturing tax credit, Treasury guidance confirms that certified projects involving the production of such materials as polysilicon, ingots, and wafers were determined to be eligible for the credit.<sup>5</sup> Notably, the solar panel manufacturing process is comparable to the production process for semiconductors, which supports the conclusion that the above-referenced materials similarly be included in the definition of "semiconductor," and therefore qualify for the section 48D credit.

In addition, while the proposed definition of "semiconductor" is broad and appears to encompass systems for quantum computing, such systems are not expressly referenced in the Proposed Regulations. SIA urges Treasury to consider revising the definition to clarify this point by adding "quantum electronics" to the illustrative list of devices and systems.

B. "Semiconductor Manufacturing" and "Semiconductor Manufacturing Processes," including "Packaging"

Treasury should revise the definition of "semiconductor manufacturing" and "semiconductor manufacturing processes" (§ 1.48D-2(I)) to include all stages of "packaging" (i.e., "back-end" manufacturing), consistent with the definition in the proposed regulations of the Department of

<sup>5</sup> § 48C(c)(1)(A)(i)(I). The White House Fact Sheet announcing awardees of the clean energy manufacturing tax credit under section 48C includes a list of certified applications and certified projects by the Internal Revenue Service, which includes projects for polysilicon, ingots, wafers, etc. *See, e.g.*, Hemlock Semiconductor Corp., SolarWorld Industries America, Inc., Sumco Phoenix and Wacker Polysilicon North America LLC. See <a href="https://obamawhitehouse.archives.gov/the-press-office/fact-sheet-23-billion-new-clean-energy-manufacturing-tax-credits">https://obamawhitehouse.archives.gov/the-press-office/fact-sheet-23-billion-new-clean-energy-manufacturing-tax-credits and https://obamawhitehouse.archives.gov/sites/default/files/100108-48c-selection-final-with\_projects.xls.</a>

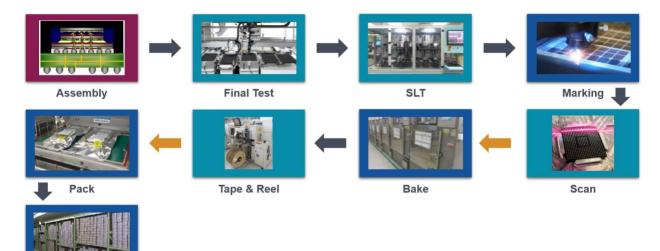

Commerce ("Proposed Commerce Regulations"), which is incorporated by reference in the Proposed Regulations (§ 1.48D-2(I)(1)).<sup>6</sup> In particular, Treasury should clarify that the definition of semiconductor "packaging" also includes the process of "assembly" and "test" of semiconductors (§ 1.48D-2(I)(2)(i)).

Once hundreds of chips are fabricated on a wafer, the next step is to separate the individual chips, test them, and assemble them in a "package" to prepare it for mounting onto a circuit board and incorporation into a finished assembly or product. The assembly, test, and packaging (ATP) stage is commonly known within the industry as "back-end" manufacturing. Each of these steps are integral parts of the manufacturing process as manufacturers must assemble, test, and package an individual device to ensure the product meets customer specifications. We respectfully request that Treasury expand the examples listed in the Proposed Regulations (§ 1.48D–3(f)) to confirm the inclusion of back-end manufacturing equipment (i.e., that related to assembly, testing, and packaging) to ensure consistency and transparency of what is considered "semiconductor manufacturing" and the types of property eligible under section 48D.

Additionally, "semiconductor manufacturing" should include in its definition compound semiconductor formation processes such as crystal growth, wafer singulation, and epitaxy and the production and purification of polysilicon and silicon carbide, as well as monosilicon ingots, boules, and wafers manufactured from semiconductive substances (such as polysilicon and silicon carbide). This addition aligns with SIA's proposed definition of "semiconductor" to include mono or polycrystalline solid substances with electronic properties manufactured specifically for the purpose of semiconductor manufacturing.

C. "Semiconductor Manufacturing Equipment"

The Proposed Regulations generally adopt a broad definition of "semiconductor manufacturing equipment" (§ 1.48D-2(m)) and list a number of examples of such equipment (§1.48D-2(m)(1) through (7)). SIA supports this definition and requests it be further clarified. The list of examples in the definition should be framed as a non-exclusive one. Accordingly, the sentence immediately preceding § 1.48D-2(m)(1) should be modified to read as follows: "Specific examples of semiconductor manufacturing equipment and subsystems that enable semiconductor manufacturing equipment include, *but are not limited to* . . . ." SIA requests that Treasury expand the list to provide taxpayers with more certainty in claiming the credit. A proposed list of qualified property to be included can be found in Appendix A.

Furthermore, the list of property in § 1.48D-2(m) appears to reference only finished equipment and does not address the term "subsystems." Subsystems included in semiconductor equipment manufacturing, such as lenses and photomasks, are both necessary and primarily applicable to the production of semiconductor chips. These subsystems are customized, with months-long production timelines, and of the highest durability in that these lenses and photomasks must be able to withstand billions of laser pulses. These lenses are directly responsible for the lasers used in photolithography, metrology, and inspection. The lenses and

<sup>&</sup>lt;sup>6</sup> Preventing the Improper Use of CHIPS Act Funding, CHIPS Program Office, National Institute of Standards and Technology, Department of Commerce, 88 Fed. Reg. 17439 (Proposed Reg. March 23, 2023) (to be codified at 15 CFR 231) at § 231.118.

mirrors are produced from glass boules, are shaped, polished, and coated to customer specifications, and are housed in mechanical assemblies in order to locate and align the beams directed through them. These manufacturing processes are generally not automated and instead require highly skilled workers to produce them through meticulous precision and testing. Depending on the final piece of manufacturing equipment, these sub-assemblies are built into larger subsystems that are integrated into a larger "box" (i.e., the finished piece of equipment) along with other subsystems. Perhaps most importantly, such subsystems are produced only for use in semiconductor manufacturing equipment made specifically to manufacture semiconductor chips.

Accordingly, we recommend that Treasury include in its definition of subsystem 1) specialty glass lenses (e.g., high-purity fused silica or ultra-low expansion glass) and photomasks used by photolithography machines to etch chip designs, 2) lenses and mirrors, like those made of calcium fluoride or high-purity fused silica, that enable the laser light source for wafer flatness inspection equipment (i.e., "laser optics"), 3) lens assemblies for wafer defect inspection following wafer printing (i.e., "precision optics"), and 4) light sources or other major components of photolithography systems.

D. Partnership Basis Allocations and "Applicable Taxpayer" in the Partnership Context

In North America, semiconductor companies may enter into partnerships with third parties (e.g., financial institutions) to engage in large scale semiconductor manufacturing projects and help optimize their investments in new chip manufacturing. Often, these arrangements are structured as partnerships under which only one partner is intended to take advantage of the section 48D credit (i.e., claim 100 percent of the credit), notwithstanding the fact that the partnership itself is funded by the contributing partners in some other ratio (e.g., 50%/50%). The Proposed Regulations specify that for purposes of the apportionment of basis between partners, rules under Treas. Reg. § 1.46-3(f) will apply. Those rules generally require that partners' shares of the partnership's basis in qualified property will be determined in accordance with the ratio in which the partners divide the general profits of a partnership.<sup>7</sup> Thus, in the instance of a 50/50 joint venture, the partners would each share 50 percent of the basis in the partnership's income. Of course, this would frustrate the intent of the partners in the partnership that only one partner claim the full section 48D credit, as the basis allocation would limit the extent to which the credit could be claimed to 50 percent.

To allow unrelated parties entering into joint ventures to structure the section 48D credit benefit as they wish, SIA proposes that § 1.46-3(f) be modified to permit the allocation of the partnership's basis in qualified property to partner(s) independent of the ratio in which the partnership's general profits are allocated amongst the partners. In no circumstances would the partnership's basis in qualified property be allocated to a partner who would not otherwise be entitled to claim the credit if it were to undertake the same activities it undertook within the joint venture on its own. Further, SIA recommends that the partner(s) to whom the basis is allocated – and who therefore actually claim the section 48D credit – be treated as the applicable

<sup>&</sup>lt;sup>7</sup> Treas. Reg. § 1.46-3(f)(2)(i).

taxpayer for purposes of the recapture rules proposed under § 1.50a-2 (rather than the partnership), because activities undertaken outside the context of the joint venture by an unrelated partner should not operate to trigger recapture of the section 48D credit claimed by another partner who is party to the joint venture.

## II. Qualified property. (§ 1.48D-3)

A. Calculating basis in a dual-use facility

The statute specifies that qualified property "includes any building or its structural components which otherwise satisfy the requirements" of the Act and excludes "a building or portion of a building used for offices, administrative services, or other functions unrelated to manufacturing."<sup>8</sup> This provision underscores Congress's intent to broadly define qualified property to include any building or its structural components needed for semiconductor fabrication or equipment manufacturing, with the limited exception of accompanying offices.

In excluding portions of a building used for offices, Treasury should distinguish true back-office type functions unrelated to manufacturing (e.g., payroll, accounting, etc.) from office space supporting the operations of the manufacturing facility (e.g., direct supervision, management, support services, and procurement). Accordingly, Treasury should deem the basis attributable to reasonably identifiable portions of a building, including office space, as well as research and storage facilities mentioned in § 1.48D-3(f)(2), that are integral to manufacturing semiconductors or semiconductor manufacturing equipment to be treated as qualified property and therefore eligible for the credit. Office space properly characterized as qualified property might include (but is not limited to), for example, offices housing functions such as:

- Facilities teams to maintain the clean room systems integral to semiconductor manufacturing;

- Environmental Health and Safety ("EHS") teams to ensure the safety of both the people and the environment during the manufacturing process;

- IT infrastructure/data processing directly related to the manufacturing process, such as systems in support of automated processes, equipment and process monitoring, and operational systems; and

- Facilities for workforce training centers directly related to manufacturing semiconductors or semiconductor manufacturing equipment.

Further, the Proposed Regulations treat offices devoted solely to administrative functions as outside the scope of the credit. In the case of a dual-use facility, SIA respectfully requests additional guidance on how to apportion basis between portions of the facility that are and are not considered "qualified property" ( $\S$  1.48D-3(c)(2)). For any portion of a building and its structural components that is excluded from the term "tangible depreciable property" pursuant to  $\S$  1.48D-3(c)(2), Treasury should allow taxpayers to utilize any reasonable method to apportion the basis and offer examples of methods that are considered reasonable to determine the apportionment of the basis attributable to the excluded property.

<sup>&</sup>lt;sup>8</sup> § 48D(b)(2)(B)(ii).

For example, one method Treasury should consider is the apportionment of the basis in buildings and structural components based upon square footage at the time of placement into service. Another method Treasury should consider is an actual allocation of costs of building and structural components among the portion utilized for manufacturing actives and the portion utilized for other functions unrelated to manufacturing. Treasury could also provide a safe harbor similar to that included in the UNICAP regulations addressing dual function storage.<sup>9</sup> In that context, the regulations establish a de minimis 90-10 rule providing that if 90 percent or more of the costs of a facility are attributable to the on-site storage function, the entire storage facility is deemed to be an on-site storage facility. Similarly, if 90 percent or more of the costs of an advanced manufacturing facility were determined to be integral to the manufacture of semiconductors or semiconductor manufacturing equipment, the entire building would be qualified property for purposes of section 48D.

Finally, while the Proposed Regulations do exclude property related to administrative functions from the qualified property definition, they do allow for property related to cybersecurity operations to be eligible for the credit. We support Treasury's treatment of cybersecurity operations, due to the highly sensitive nature of semiconductor manufacturing.

B. Request for a transition rule for calculating basis after date of enactment

Section 107(f) of the Act provides that, in general, the advanced manufacturing investment credit "shall apply to property placed in service after December 31, 2022." The language goes on to state that the credit shall apply to "any property the construction of which begins prior to January 1, 2023, only to the extent of the basis thereof attributable to the construction, reconstruction, or erection after the date of enactment of this Act." Taxpayers will benefit from some flexibility on this point because of difficulties associated with tracking and allocating costs around a date occurring in the middle of a month—that is, the date of enactment on August 9, 2022.

SIA therefore requests that the final regulations provide a transition rule where taxpayers may use any reasonable method to allocate costs to periods after August 9, 2022. Existing Treasury regulations frequently allow taxpayers to use "any reasonable method" to make determinations for which a taxpayer may not have the ability or data. Relevant examples relating to the investment tax credit include those for rehabilitation expenditures under 1.48-11(b)(5)(i), where any reasonable method may be used to allocate property that services different portions of a building between the qualified rehabilitated portions of a building, or 1.48-12(c)(1), where a taxpayer may use any reasonable method to allocate qualified rehabilitation expenditures between an original building and an enlargement.

<sup>&</sup>lt;sup>9</sup> See Treas. Reg. § 263A-3(c)(5)(iii)(C).

C. "Original use" (§ 1.48D-3(e))

Semiconductor manufacturing and packaging facilities routinely fabricate and package chips using second-hand, refurbished equipment. Accordingly, SIA requests that Treasury revise the Proposed Regulations' definition of "original use" such that it includes acquired property that is reconditioned or rebuilt by another taxpayer, without a requirement that the acquiring taxpayer subject such property to further reconditioning or rebuilding before it may claim the section 48D credit. Such a result is appropriate where the property (e.g., lithography systems) has a long useful life. One manufacturer of semiconductor equipment estimates that 96% of its machines ever produced currently remain in service, and that manufacturer has been producing the equipment for nearly 40 years.<sup>10</sup> Due to the quality and continued value of the equipment, coupled with the high cost of acquiring such systems, using reconditioned or rebuilt equipment is a common practice in the industry, and such property should be covered under 48D.

D. Clarify certain circumstances surrounding leased property (§ 1.48D-3(e))

Leasing is a form of financing that is critical to the semiconductor manufacturing industry given the high capital expenditure requirements, and it is unclear how the Proposed Regulations would apply to the taxpayer's use of leased property that the taxpayer reconditions or rebuilds. Former section 48(d) provided rules with respect to leased property and taxpayers currently rely on section 50(d)(5) and Treas. Reg. § 1.48-4 to make lease elections for eligible investment tax credit property. Consistent with the statutory authority under section 50(d)(5),<sup>11</sup> Treasury should provide that Treas. Reg. § 1.48-4 also applies for purposes of section 48D and should specify the requirements for a lessor to elect to treat the lessee of leased property as the owner of such property for purposes of section 48D.

In the absence of specific rules in line with the section 48 guidance outlined above, Treasury should at least consider clarifying that a taxpayer's lease of an advanced manufacturing facility that the taxpayer subsequently reconditions, rebuilds, or purchases constitutes "original use" of the property for purposes of section 48D. As a part of this additional guidance, SIA proposes including illustrative examples, including those addressing the issue of which taxpayer – the lessee, the lessor, or the lessee who purchases the previously leased facility and subsequently reconditions and/or rebuilds it – is eligible to claim the credit under these circumstances.

E. Further clarification of qualified property integral to the operation of a manufacturing facility (§ 1.48D-3(f))

Section 48D(b)(2)(iv) provides that qualified property must be "integral to the operation of the advanced manufacturing facility." SIA generally supports Treasury's proposed coverage of the types of investments in qualified property that are integral to the operation of an advanced

<sup>&</sup>lt;sup>10</sup> Tarasov, K. (2022, March 23). ASML is the only company making the \$200 million machines needed to print every advanced microchip. Here's an inside look. CNBC. https://www.cnbc.com/2022/03/23/inside-asml-the-company-advanced-chipmakers-use-for-euv-lithography.html

<sup>&</sup>lt;sup>11</sup> Providing that, for purposes of subchapter A, part IV, subpart E of the code (which includes section 48D), rules similar to those under section 48 (as in effect prior to the enactment of the Revenue Reconciliation Act of 1990) regarding the treatment of leased property shall apply.

manufacturing facility.<sup>12</sup> As a general matter, the Proposed Regulations properly encompass the full range of investments in buildings, infrastructure, and equipment for the equipping, construction, expansion, or modernization of a semiconductor fabrication facility ("fab") or a facility producing semiconductor manufacturing equipment. SIA believes the Proposed Regulations are construed broadly to include site preparation, construction of the manufacturing facility, equipment, automation, test tools, accompanying infrastructure—like piping and storage systems, purification, pollution, lighting, and temperature control systems—and similar property integral to the operation of an advanced manufacturing facility.

In the Proposed Regulations, Treasury provides what appears to be a non-exhaustive list of qualified property considered to be eligible for the section 48D credit. To increase taxpayer certainty in claiming the credit, Treasury should clarify that the list is illustrative and does not encompass the full universe of property that may be deemed to be integral to the operation of the facility. Accordingly, the sentence immediately preceding § 1.48D-3(f)(1) should be modified to read as follows: "Specific examples of property which normally would be integral to the operation of the advanced manufacturing facility of an eligible taxpayer *include, but are not limited to* ...."

SIA respectfully requests that Treasury also expand the non-exhaustive list of qualified property included in the final regulations to include the types of property listed in Appendix A (note, however, that such list does not constitute an exhaustive list of all property that could be considered qualified property under section 48D). For example, we request qualified property include emulation tools and photomasks/reticles. These additional examples, like others in the Appendix A, are "tangible depreciable property that is integral to the operation of an advanced manufacturing facility," are used "in connection" with manufacturing, and are "essential to the completeness of the manufacturing operation." We note that the Proposed Regulations already include "reticle handlers," "mask manufacturing equipment," and "inspection and metrology equipment" among the examples of qualified property, but these terms do not encompass emulation tools or photomasks/reticles. We note below the special functions of each of the above-enumerated types of property in an effort to distinguish them from the property already included in the Proposed Regulations and illustrate how they rise to the level of qualified property property property property deemed eligible for the section 48D credit.

- Emulation hardware is a type of electronic hardware used for testing and debugging digital systems or electronic designs. It allows engineers to verify and validate the functionality of a design before the actual hardware is produced. One of the key benefits of using emulation hardware is that it allows engineers to identify and fix problems that may be inherent to the design, which can help to reduce the overall development time and cost.

- During the lithography process, the patterned mask is placed over the substrate, and a beam of light is directed through it to transfer the pattern onto the substrate. The light

<sup>&</sup>lt;sup>12</sup> Property is integral to the operation of manufacturing semiconductors or semiconductor manufacturing equipment if such property is used directly in the manufacturing operation, is essential to the completeness of the manufacturing operation, and is not transformed in any material way as a result of the manufacturing operation" *Prop. Treas. Reg.* § 1.48D-3(f).

passing through the transparent areas of the mask will expose the photoresist on the substrate, creating a pattern that can then be etched into the substrate. The process is fundamental to the creation of the circuitry that provides for the functionality and performance of an individual chip.

Each of these items are integral to the manufacturing process, and explicitly including these inputs to the manufacturing process as qualified property is wholly consistent with congressional intent of incentivizing domestic investments in semiconductor manufacturing.

Additionally, SIA requests that Treasury clarify that the definition of "transformed" in the Proposed Regulation (§ 1.48D-3(f)) does not include the normal degradation of components of semiconductor manufacturing equipment.

F. Clarify the eligibility of certain research or storage facilities

SIA supports the Proposed Regulations' inclusion of research facilities, such as those used in pre-pilot production or prototyping, in the definition of qualified property insofar as they are deemed "integral to the operation of the advanced manufacturing facility under section 48D(b)(2)(A)(iv)."<sup>13</sup> Many companies have production facilities—fabs, ATP facilities, semiconductor manufacturing equipment facilities, and design—and research and development (R&D) operations, which may or may not share buildings, infrastructure, and equipment, to ensure new design and/or product technology is developed and transitioned into a prototype or pilot manufacturing setting. This part of the process is to ensure a particular technology can be scaled for commercial production. Due to the rapidly advancing technologies used in the semiconductor industry, R&D facilities are critical to certain manufacturers to optimize the time to market for new technologies and are an integral component to semiconductor manufacturing regardless of whether they are co-located with a manufacturing facility.

However, the Proposed Regulations further note that research facilities do not qualify if they do not manufacture any type of semiconductor or semiconductor manufacturing equipment.<sup>14</sup> This restriction goes beyond the statutory language, which only excludes buildings, or portions thereof, that are "unrelated" to manufacturing. SIA recommends that Treasury should treat these types of facilities as advanced manufacturing facilities, notwithstanding potential co-location within a single structure.

As currently drafted, the Proposed Regulations exclude certain research facilities which are integral to the operation of semiconductor manufacturing, used "in connection" with manufacturing, and are essential to "the completeness of the manufacturing operation." We believe the Proposed Regulations exclude certain research facilities that should otherwise qualify for the credit and request the last sentence of § 1.48D-3(f)(2) be changed to read "a research facility that is not used in connection with the manufacture of any type of semiconductors, as provided in § 1.48D-2(k), or semiconductor manufacturing equipment, as provided in § 1.48D-2(m), does not qualify."

<sup>&</sup>lt;sup>13</sup> See Prop. Treas. Reg. § 1.48D-3(f)(2).

<sup>&</sup>lt;sup>14</sup> Id.

In regard to storage facilities, the Proposed Regulations list examples to include "mineral, chemical, and gas storage tanks, including high pressure cylinders or specially designed tanks and drums,"<sup>15</sup> but do not explicitly include semiconductor equipment parts storage used in regular maintenance. Such storage for equipment replacement, repair, and cleaning, and other storage used to maintain advanced manufacturing facilities should be included so as to fully encompass the scope of storage facilities integral to the operation of semiconductor manufacturing and semiconductor equipment manufacturing.

#### III. Advanced manufacturing facility of an eligible taxpayer. (§ 1.48D-4)

A. Strike, or define, the term "finished" as applied to "semiconductor" and "semiconductor manufacturing equipment"

There are several references throughout the Proposed Regulations to the term "finished semiconductor" and "finished semiconductor manufacturing equipment" *(see, e.g.,* Prop. Treas. Reg. § 1.48D-3(f), -4(b) and -4(c)), but the term is not defined. SIA recommends Treasury strike the word "finished" as applied to "semiconductor" and "semiconductor manufacturing equipment" in the Proposed Regulations everywhere it appears so as to avoid inadvertently disqualifying otherwise qualifying expenditures, property, or facilities. Without such adjustment, the term may exclude output from a broad range of semiconductor fabrication and semiconductor manufacturing equipment facilities.

For example, assume a semiconductor fab produces a patterned wafer consisting of hundreds of individual semiconductor devices, which comprises a significant portion of the overall value of the entire manufacturing process. Arguably, the patterned wafer is not a "finished semiconductor." The fabricated wafer remains an interim product that awaits additional processing before it is ready to be incorporated into a larger component (e.g., a circuit board) or a final product (e.g., a cell phone, a laptop, etc.). In another common scenario, consider a complex piece of semiconductor manufacturing equipment. The equipment may be shipped from a semiconductor manufacturing equipment facility to another semiconductor manufacturing equipment facility to another semiconductor fab prior to the equipment being fully operational. In this example, a lithography tool may be shipped with the primary light source and top module intact and then undergo additional assembly or upgrades at another manufacturing facility. Chipmakers do not purchase these distinct components produced by the semiconductor manufacturing equipment facility; they purchase the complete lithography system that is later assembled.

It is evident that both Congress and Treasury intended for the fabrication of semiconductor wafers and production of semiconductor manufacturing equipment to be eligible for the section 48D credit, but the reference to "finished" semiconductors and manufacturing equipment injects uncertainty as to what property qualifies for the section 48D credit. Accordingly, SIA recommends that the term "finished" as applied to "semiconductor" and "semiconductor manufacturing equipment" be stricken from the final regulations.

<sup>&</sup>lt;sup>15</sup> Prop. Treas. Reg. § 1.48D-3(f)(2).

As an alternative and at minimum, Treasury should expand § 1.48D-2 to include a definition of the term "finished" to better reflect the states of a semiconductor or the various types of semiconductor manufacturing equipment when such property leaves a manufacturing facility. It is critical that this new term is clarified to include various forms of output from semiconductor manufacturing facilities (i.e., semiconductor wafers that have been produced as output from the fabrication process) and semiconductor equipment manufacturing facilities. Treasury should also explicitly state that "back-end" and "front-end" functions do not need to occur within the same facility. In other words, "finished semiconductor" should be defined to include both wafers from a front-end fabrication facility as well as modules and components from a back-end assembly, test, and packaging facility.

#### B. "Primary purpose" threshold test

In the Proposed Regulations, Treasury states that the "primary purpose" of a facility will be determined on a facts and circumstances basis, whereby taxpayers must demonstrate that a facility is designed to make semiconductors or "products consisting of specialized equipment that can only be used for semiconductor manufacturing." Treasury lists two examples, both of which use a 75 percent threshold to illustrate circumstances where a facility may satisfy the test (§ 1.48D-4(c)). We request that Treasury consider implementing a safe harbor under which the facility's primary purpose will be considered to be the manufacture of semiconductors or semiconductor manufacturing equipment if more than 50 percent of its functions are devoted to such activities. This change would help to accommodate dual-use facilities that may manufacture other types of equipment not exclusive to the semiconductor industry. Additionally, SIA suggests that Treasury provide examples of what is not considered a facility meeting the "primary purpose" test, especially for facilities that do not meet the 75 percent threshold.

C. "No primary purpose"

As stated above, the definition of the term "semiconductor" should be revised to include polysilicon, boules, wafers, and similar materials with electronic properties manufactured specifically for the purpose of semiconductor manufacturing (§ 1.48D-2(k)). If this expanded definition is adopted, we recommend striking the words "grows" and "grow wafers" in Prop. Treas. Reg. § 1.48D-4(c)(2).

#### IV. Beginning of construction. (§ 1.48D-5)

The Proposed Regulations specify that the section 48D credit applies to an advanced manufacturing facility the construction of which begins prior to December 31, 2026 (§ 1.48D-5(a)). SIA generally supports this approach adopted by Treasury, but we request further clarification and guidance with respect to certain provisions under this section.

A. "Single advanced manufacturing facility project" (§1.48D-5(a)(3))

The beginning of construction rules provided in the Proposed Regulations have largely been borrowed from the body of guidance for beginning construction that is applicable to energy tax credits. However, because of the nature and composition of energy projects and semiconductor manufacturing projects are different, it is recommended that the Proposed Regulations include some clarifications in the wording that are necessary to make the language clearly applicable to

the totality of advanced manufacturing projects. In particular, language in Prop. Treas. Reg. § 1.48D-5(a)(3) describes what constitutes a single advanced manufacturing facility project and lists included items considered integral to the operation of a "single advanced manufacturing facility project." It is recommended that the proposed language in Prop. Treas. Reg. §1.48D-5(a)(3) be amended to include "tooling equipment (such as for deposition, etching, etc.)" within the list that includes "…clean rooms, chemical delivery systems, chemical storage facilities, temperature control systems, and robotic handling systems…"

B. Additional examples of onsite and offsite activities deemed to meet the physical work test (§ 1.48D-5(c))

Under existing guidance<sup>16</sup> and the Proposed Regulations, there are two methods for establishing when construction begins: the Physical Work Test and the Five Percent Safe Harbor, with a continuity requirement underpinning both methods. SIA generally supports the guidance with respect to determining when construction has begun and the clarifications around estimating costs for purposes of satisfying the Five Percent Safe Harbor. However, to provide taxpayers with further certainty, we request Treasury provide additional guidance with respect to onsite and offsite activities specific to the manufacturing of semiconductors and semiconductor manufacturing equipment that would satisfy the Physical Work Test.<sup>17</sup>

C. "Continuous efforts" test (§ 1.48D-5(e)(3))

The construction of advanced manufacturing facilities is a complex process, and the lead time for construction is much longer than that for many other types of manufacturing facilities. Moreover, market volatility and the cyclical nature of semiconductors, paired with the extraordinarily high cost of building a new advanced manufacturing facility, are all factors that may delay construction in a market downturn. Congressional intent in enacting the advanced manufacturing investment credit was to create a robust and long-lived semiconductor ecosystem, and to afford taxpayers ample opportunity to avail themselves of the credit for ongoing projects.<sup>18</sup> We commend Treasury in recognizing the unique nature of constructing a semiconductor manufacturing facility and providing a 10-year safe harbor for that purpose (§ 1.48D-5(e)(6)). However, for some facilities, like those built in sequential phases to encompass multiple fabs in a single project, construction may extend beyond 10 years.

In the case where the 10-year safe harbor is not met, we request Treasury provide examples of the facts and circumstances that would support the conclusion that the taxpayer satisfied the

<sup>&</sup>lt;sup>16</sup> See Internal Revenue Service, Notice 2018-59: "Beginning of Construction for the Investment Tax Credit Under Section 48," *available at* https://www.irs.gov/pub/irs-drop/n-18-59.pdf (hereinafter Notice 2018-59).

<sup>&</sup>lt;sup>17</sup> See, e.g., Notice 2016-31, Notice 2018-59, Notice 2020-12 (providing examples of "physical work of a significant nature" for purposes of the physical work test that are specific to various technologies and industries covered by tax credits under §§ 45, 45Q, and 48).

<sup>&</sup>lt;sup>18</sup> Office of U.S. Senator Charles E. Schumer (2023, February 24). Schumer pushes feds for swift implementation of investment tax credit created in his CHIPS & Science Act to get shovels in the ground and boost semiconductor industry jobs in upstate NY, available at <u>https://www.schumer.senate.gov/newsroom/press-releases/schumer-pushes-feds-for-swift-implementation-of-investment-tax-credit-created-in-his-chips-and-science-act-to-get-shovels-in-the-ground-and-boost-semiconductor-industry-jobs-in-upstate-ny.</u>

"continuous efforts" test. For example, paying or incurring additional amounts included in the total cost of the property is considered indicative of such continuous efforts.<sup>19</sup>

C. Ensure that the continuity safe harbor is not less than the prescribed 10-year period

The semiconductor manufacturing industry employs almost exclusively equipment that is not widely manufactured and is ordered several years in advance of beginning substantial on-site construction of a manufacturing facility. Site preparation for semiconductor manufacturing may also be considered physical work of a significant nature under established beginning of construction principles even though on-site construction has not begun in earnest. In the semiconductor industry, long-lead procurement of custom equipment and project-specific onsite work early in the development cycle is a common occurrence.

Given the long-lead procurement of custom equipment and early project-specific site work inherent in the development of semiconductor manufacturing facilities, taxpayers constructing such facilities may trigger the "beginning of construction" earlier in the development cycle thereby "starting the clock" for the ten-year safe harbor during which a taxpayer must place the qualified property in service. The structure of a continuity safe harbor that measures from the beginning of construction, in the context of semiconductor manufacturing, creates a perverse incentive to intentionally delay the beginning of construction date to as late in 2026 as possible so as to more closely align the time that construction actually begins (as opposed to site preparation activities) to the beginning of the tolling of the 10-year safe harbor period.

We recommend addressing these issues by creating a simple and bright-line approach of a fixed date for the continuity safe harbor, and recommend utilizing December 31, 2036, which is 10 years after the beginning of construction deadline. There is precedent for taking this approach, as a similar rule was imposed in the regulatory guidance amplifying the renewables production tax credit.<sup>20</sup> Given that the tax credit under section 48D does not have a long-term qualification period and does not contain a phase-down period, it would be appropriate to provide taxpayers with the certainty afforded by a fixed placement in service deadline with respect to the continuity safe harbor.

D. Support for excusable disruptions to continuous construction (§ 1.48D-5(e)(4))

SIA supports the inclusion of provisions allowing for excusable delays that could potentially impact a taxpayer's continuous efforts tests (§ 1.48D-5(e)(4)). We appreciate Treasury's acknowledgement that certain disruptions to construction may inevitably occur in large-scale projects, and such unforeseen events should not operate to deprive a taxpayer of eligibility for the credit for otherwise ongoing, continuous construction. The proposal properly enumerates several non-exclusive examples of excusable disruptions, ranging from weather and natural disasters to delays in permitting approvals, supply chain disruptions, and financing.

<sup>&</sup>lt;sup>19</sup> Prop. Treas. Reg. § .48D-5(e)(3)(i).

<sup>&</sup>lt;sup>20</sup> See Notice 2013-60, Section 3.02 and Notice 2015-25 Section 3.

# V. Recapture of the advanced manufacturing investment credit in the case of certain expansions. (§ 1.50-2)

Section 107(b) of the CHIPS Act provides for the "recapture" of the advanced manufacturing tax credit for an "applicable transaction" during the 10-year period from the placement into service of property eligible for the credit. The Act defines an "applicable transaction" as "any significant transaction . . . involving the material expansion of semiconductor manufacturing capacity" by the taxpayer in China or a foreign country of concern (IRC 50(a)(3)(D)(i)). The Act provides for an exception for "a transaction which primarily involves the expansion of manufacturing capacity for legacy semiconductors" (IRC 50(a)(3)(D)(ii)). Consistent with the direction by Congress for Treasury to define "applicable transaction" subject to recapture "in coordination with the Secretary of Commerce and the Secretary of Defense," the proposed regulations by Treasury implementing these provisions largely parallel the Proposed Commerce Regulations implementing the CHIPS grant "clawback" provisions.<sup>21</sup>

The recapture in the Proposed Regulations (as with the "guardrails" in the Proposed Commerce Regulations) were enacted in recognition of the complex role of China in the global semiconductor ecosystem, the global supply chain and economy as a whole, and the national security landscape. In the semiconductor industry, China is simultaneously (1) an enormous market, comprising approximately one-third of all chip sales from U.S. companies, (2) a major part of the semiconductor supply chain, with about 20 percent of front-end capacity and nearly 40 percent of back-end capacity, and (3) a major competitor, with a growing industry in all segments of semiconductor research, design, fabrication, packaging, equipment, and materials. Given this multifaceted and complex relationship, Congress constructed a balanced statutory framework to work alongside other policies (e.g., export controls) to ensure that, as the U.S. provides incentives to attract investments in new semiconductor fabrication and equipment manufacturing facilities to strengthen the economy and make the domestic supply chain more resilient, it would restrict certain new investments in China to address national security concerns and supply chain dependence. The "recapture" provision established under the advanced manufacturing investment credit curtails tax credit recipients' ability to increase advanced semiconductor manufacturing capacity in China, while simultaneously allowing for the continued operation of existing legacy facilities or the construction of new or expanded legacy facilities predominantly serving the China market. Congress sought to allow the continued operation of legacy facilities in China to avoid causing disruption to the global chip supply chain. In executing this complex framework in the Proposed Regulations, however, we believe Treasury, in certain instances, did not strike the right balance. Some aspects of the Proposed Regulations jeopardize the continued commercial viability of existing legacy operations in China of companies based in the U.S. and allied countries, which could potentially result in supply chain disruptions in the global semiconductor industry and harm the commercial competitiveness of the semiconductor industry.

<sup>&</sup>lt;sup>21</sup> Proposed 15 C.F.R. Part 231, 88 Fed. Reg. 17439 (March 23, 2023).

A. SIA supports the overall consistency and alignment between Commerce and Treasury proposals but additional alignment is still required

SIA supports the overall consistency between the Proposed Regulations and the Proposed Commerce Regulations, as reflected in the recapture and guardrails provisions, respectively. SIA has filed extensive comments with respect to the "guardrails" provisions under the Proposed Commerce Regulations. We attach these comments (see Appendix B) and incorporate them by reference into this letter. We respectfully request that Treasury revise the recapture proposal to be consistent with SIA's proposed revisions to the Proposed Commerce Regulations addressing the guardrails. An aligned set of restrictions on transactions in foreign countries of concern, where applicable, is needed to facilitate compliance with these requirements and reduce administrative burdens, particularly for companies who are both direct funding recipients under the CHIPS incentive program and eligible for the advanced manufacturing investment credit under section 48D. Alignment of the two regulatory requirements will also provide for the more efficient use of government resources.

Further, these revisions are needed to better advance the intent of Congress in enacting the guardrails/recapture requirements: that being, as the CHIPS incentives are being deployed to strengthen the domestic ecosystem, these incentives, while still allowing for the continued commercial viability of existing legacy facilities in countries of concern, should not be used to subsidize investments in foreign countries of concern. Certain provisions in the proposal should be revised to accommodate the continuation of operations at existing legacy facilities in countries of concern needed to ensure they remain operational and competitive. In other words, while both the Treasury "recapture" and Commerce "expansion clawback" rules should operate to restrict new construction or significant expansions of manufacturing capacity in foreign countries of concern, as well as any increase in manufacturing capacity of advanced semiconductors, these prohibitions should avoid disrupting ordinary business activities (e.g., maintenance, the replacement or upgrade of equipment, etc. that do not involve new construction or the physical expansion of a facility) at existing legacy facilities, especially given the length of time of the advanced manufacturing investment credit recapture period.

B. Request consistency/alignment in reporting and documentation requirements, audit procedures, and related matters

The Proposed Regulations consider recordkeeping and reporting requirements to ensure compliance with the law, with a particular view toward ensuring that the IRS is informed of taxpayers' engagement in "applicable transactions." The Proposed Regulations further state that Treasury and the IRS will coordinate with the secretaries of Commerce and Defense to determine whether a transaction is an applicable transaction, which is defined to be consistent with the Proposed Commerce Regulations.

The Proposed Regulations include a request for comments on taxpayers' ability to comply with such requirements and what procedures should be utilized in determining if a taxpayer engages in an applicable transaction. For taxpayers receiving direct funding under the Commerce program, due consideration should be given to the burden taxpayers will bear in reporting to both Treasury and Commerce on what may be the same information regarding a planned applicable transaction. SIA respectfully requests that Treasury and Commerce streamline the

reporting and recordkeeping requirements so as to not be duplicative and overly burdensome on the taxpayer participating in both incentive programs enacted under the CHIPS Act.

Specifically, SIA encourages Treasury and Commerce to consider adopting guidelines similar to those of the Executive Order: Reorganization Plan No. 4 of 1978, whereby the Secretary of Labor transferred certain enforcement authority for overlapping regulations to the Secretary of the Treasury. While both agencies still had an important role in oversight, the Executive Order delegated responsibility for administering the various overlapping rules to a single agency. This action would be equally appropriate in instances where companies are receiving both a grant and claiming the tax credit and therefore subject to the same restrictions in many cases. As the Proposed Regulations are intended to be "harmonized with existing oversight and restrictions on these types of transactions imposed by the Export Administration Regulations (15 CFR parts 730 through 744)," streamlining the review of the recapture of advanced manufacturing tax credit with that of the expansion clawback under the Department of Commerce would be an efficient outcome.

Additionally, the IRS could include a form or attachment to annual tax returns with basic questions for the IRS to ascertain whether an eligible taxpayer may have engaged in an applicable transaction during the taxable year.

C. Establishing to the "Satisfaction of the Commissioner" that a prohibited transaction has been abandoned

SIA recommends Treasury publish standards for establishing what is considered to be to the "Satisfaction of the Commissioner" that an applicable transaction has been abandoned and set standards for notifying a taxpayer that an applicable transaction has been entered into. The regulations or other guidance should set forth with specificity the information required by the IRS contained within its "determination and notice," which should include a description of the geographic location of the activity, the involved parties, and the nature of the activity. Further guidance should also include guidance as to how a taxpayer may demonstrate cessation or abandonment of a project. Those actions could include proof of cancelled contracts, the withdrawal or cancellation of requisite work permits, and the issuance of a public statement that expressly cancels the applicable transaction.

+ + +

SIA appreciates the opportunity to comment on this proposal and we look forward to continuing to work with Treasury in the development and implementation of these rules.

#### Appendix A Brief Overview of Semiconductor Manufacturing and Equipment Manufacturing

#### 1. Semiconductor Fabrication

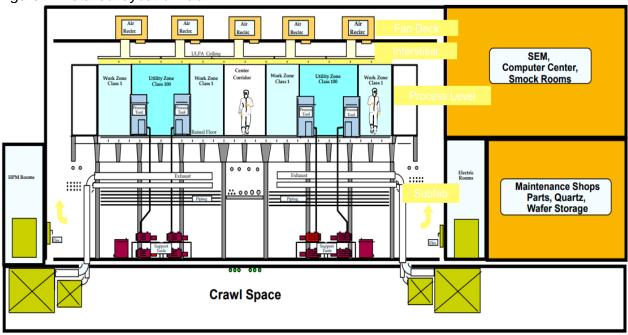

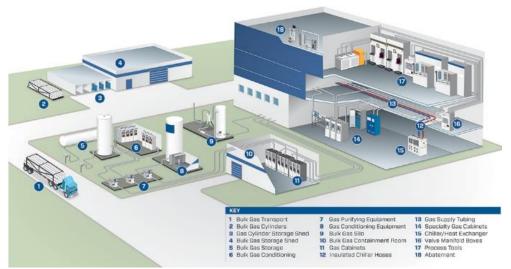

Construction of a semiconductor fabrication facility ("fab") requires qualified labor and is capital intensive. The cost of a fab can range from \$1-20 billion depending on the type and scale of the project. Construction of a fab requires highly skilled workers to build and install support systems and structures to deliver high purity gases, ultra-pure water, and state of the art air recirculation systems. A cross-section of the inside of a fab is shown below.<sup>22</sup>

Each level of the fab plays a unique role in the manufacturing process and each level requires specialized equipment, piping, clean-air, and waste management systems. Each of these systems and support structures must meet stringent requirements based on the International Standards Organization (ISO). For example, a fab clean room must meet ISO 14644-3 (updated in 2019), which applies to clean rooms and associated controlled environments that are defined as providing control of contamination to levels appropriate for accomplishing contamination-sensitive activities. Products and processes that benefit from the control of airborne

1. Interstitial and fan deck (top level)

The fan deck houses systems that keep the air in the clean room particle-free and precisely maintained at the right temperature and humidity for production. The interstitial is the tallest level of the fab.

#### 2. Clean room level

A clean room is made up of more than 1,200 factory tools that take pizza-size silicon wafers and eventually turn them into hundreds of computer chips. Clean room workers wear bunny suits to keep lint, hair and skin flakes off the wafers.

#### 3. Clean subfab level

The clean subfab contains thousands of pumps, transformers, power cabinets and other systems that support the clean room. Large pipes called "laterals" carry gaess, liquids, waste and exhaust to and from production tools. Workers don't wear bunny suits here, but they do wear hard hats, safety glasses, gloves and shoe covers.

#### 4. Utility level

Electrical panels that support the fab are located here, along with the "mains" — large utility pipes and ductwork that feed up to the lateral pipes in the clean subfab. Also here are chiller and compressor systems. Workers who monitor the equipment on this level wear street clothes, hard hats and safety glasses.

contamination include the aerospace, microelectronics, pharmaceuticals, medical devices, healthcare, and food industries.<sup>23</sup> To meet these standards, companies spend millions of dollars to install systems and support structures that adhere to ISO requirements.

Each level of a fab is integral to the overall operation of the facility. The following is a brief overview of these parts of the fab and how they and how the systems and structures installed in each level ensure an efficient manufacturing process.<sup>24</sup>

<sup>&</sup>lt;sup>22</sup> https://www.intel.com/content/dam/www/central-libraries/us/en/documents/what-does-it-take-to-build-a-fab.pdf

<sup>&</sup>lt;sup>23</sup> https://www.iso.org/obp/ui/#iso:std:iso:14644:-3:ed-2:v2:en

<sup>&</sup>lt;sup>24</sup> For an overview of the steps in the fabrication process, see White House supply chain report at 35-36.

# Fab Layout

Generally, a fab has different levels that work in coordination to filter high purity gases, chemicals, and particle free clean air. These processes occur in specialized piping systems (laterals), pumps, and abatements systems to provide purified water and waste management. These systems are necessary to support the infrastructure and equipment, like lithography machines, that produce semiconductors. Throughout the fab, specialized technicians of varying skill levels monitor these systems to ensure the smooth operation of the fab.

Figure 1: Detailed layout of Fab

Source: <u>NXP</u>

## Level 1: Interstitial and fan deck

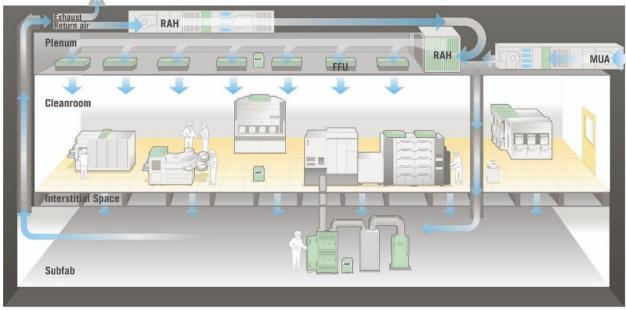

In this level of the fab, specialized recirculating air handler (RAH) units recondition the air and send it back down into the ceiling of the clean room. Clean air is supplied to each bay through a grid of high efficiency particulate air (HEPA) filters. The air flows straight down through the floor, before returning up through the floor. At the fan deck level, RAH units recondition the air and send it back down into the ceiling plenums.

In the cleanest areas, this cycle repeats 600 times per hour, and the entire ceiling is HEPA filters.<sup>25</sup> Many chemicals used in the clean room may be corrosive, so exhaust ducts from fume hoods and wet process areas are Teflon-coated, welded stainless steel. Other processes employ on-site scrubbers to treat exhaust, which then can be sent into standard ducts with vacuum pump exhaust. Exhaust removes about 10% of the air from each cycle, which is

<sup>&</sup>lt;sup>25</sup> http://www.matthewfickett.com/pdf/Poster%20-%20Cleanroom.pdf

replaced with fresh air. Hazardous process material (HPM) exhausts are often incompatible with other exhausts and must be ducted directly to a dedicated roof fan.

Figure 2: Fab Air Recirculation Structure and Support Systems

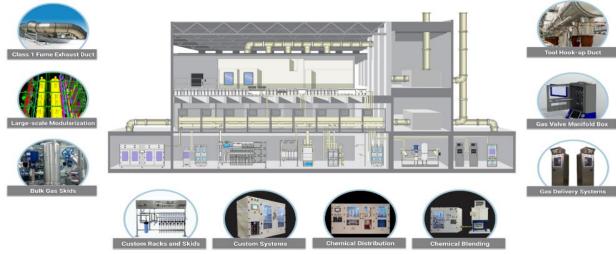

Figure 3 illustrates the many different exhaust, pipe, pump, and chemical distribution systems that are necessary for the functioning of a fab. Each system is highly specialized and must meet exacting standards before installation. For example, when working on a hook up in a facility, expertise in fluid mechanics is needed to ensure proper flow and pressure.

Figure 3: High Purity Gas/Clean Air Systems, Piping, and Chemical Distribution Systems

Source: Critical Process Systems Group

Source: Valin

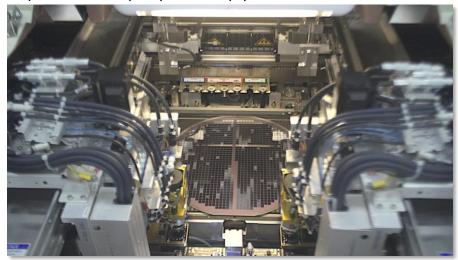

#### Level 2: Clean room

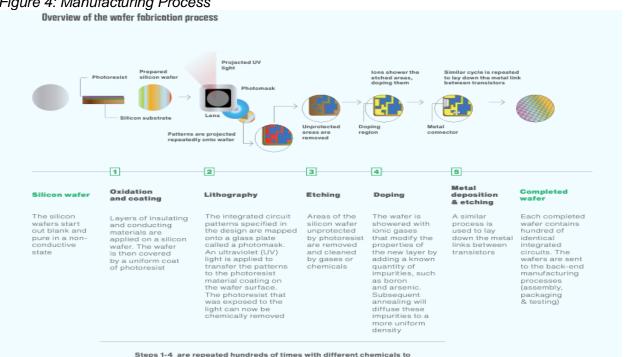

The clean room is where the front-end wafer manufacturing cycle occurs. A clean room may contain over 1000 machine tools to turn wafers to semiconductors. Figure 4 breaks down the manufacturing process and the role of each piece of equipment, and Figure 5 displays those pieces of equipment within a typical clean room. Each tool is essential to the manufacturing process and may cost in the tens of millions of dollars.<sup>26</sup> The equipment includes wet process tools, lithography equipment, analytical tools, deposition and etch tools, and stockers. Throughout the process, clean air is recirculated while sub fab level equipment continuously circulates chemical gas and ultra-pure water while simultaneously pumping out chemical waste.

#### Figure 4: Manufacturing Process

Steps 1-4 are repeated hundreds of times with different chemicals to create more layers, depending on the desired circuit features

Source: SIA/BCG Strengthening the Global Semiconductor Supply Chain in an Uncertain Era

Each process tool provides essential functions. Chemical Mechanical Polishing (CMP) valve actuation, and its impact on the integrity of the slurry is important as this will allow the system to have a more stable removal rate across a longer period. For the etching process, the precision of chemical dosing over time is critical to ensure that the chemistry used on the wafer will have the right composition, and as a result the right action. For cleaning, focusing on dispensing the exact quantity of liquid on the wafer is necessary to remove every targeted chemistry.

<sup>&</sup>lt;sup>26</sup> https://www.valin.com/semiconductor-manufacturing-process-products-and-applicability

The clean room itself is finished in non-particulating material such as epoxy paint, glass, or metal. The clean room area is arranged in bays connected by a clean corridor (shown above in Figure 1), where only gowned personnel are permitted. Between the bays, chases (picture shown to the right)<sup>27</sup> are used to access equipment. A common chase provides a location for less-clean storage or equipment. All windows and lights into the clean room are covered with a protective UV-blocking film, to avoid exposing photoresist chemicals. To

minimize vibration, the structure under the clean room must be exceptionally durable, and isolated from the rest of the building. All HVAC systems, including the ceiling plenums, are suspended from above to avoid vibrating the floor.

Figure 5: Clean room machinery

Source: Bloomberg

Protection of the clean room from contaminants is so extreme that specialized lighting systems are required. Besides dust particles from workers, lighting systems can be a source of contaminants. To eliminate these contaminants, clean rooms are typically lit with yellow or

<sup>&</sup>lt;sup>27</sup> <u>https://mitnano.mit.edu/facility-updates/cleanroom-organization-bay-vs-chase</u>

amber lighting that meet strict standards before installation.<sup>28</sup> Some requirements for lighting in

the medical-pharmaceutical industry also apply to semiconductor manufacturing.

#### Level 3: Clean room sub fab

Within the sub fab, pumps and abatement systems extract and neutralize process exhaust, deposits, and other waste materials from the clean room. Without these specialized systems, the repetitive process of producing a die on a wafer will overtime see the process degrade in performance and ultimately shutdown manufacturing. On the sub fab chemical distribution systems, expertise in fluid mechanics,

chemical compatibility (instant and over time), mechanical and pneumatic compatibility (for the pump) is needed.

In addition, the level includes ultrapure water systems, uninterruptible power supply (UPS) system, oil-free air compressors, boilers, high purity nitrogen, process cooling water and various waste systems to support the manufacturing processes.<sup>29</sup> The picture to the right shows a glimpse of the scale of just some of the piping, ducts, exhaust, and waste management systems that occupy this level of the fab. Figure 5 above details the specialized systems, structure, and machinery that are required to maintain a clean and efficient manufacturing process. Furthermore, systems like vacuum pumps and gas abatement systems, are designed to reliably serve the production process 24 hours a day and seven days a week.

#### Level 4: Utility Level

The utility level, typically housed on the bottom level but also housed on the side of the structure or within its own facility, provides services that include ultrapure water, bulk high purity gases such as nitrogen and argon, exhaust gas handling and disposal, and clean room air systems. Figure 6 list those systems that are located in the utility space.

<sup>&</sup>lt;sup>28</sup> <u>https://www.lindner-group.com/en/news/detail/photolithography-led-amber-light-for-clean-rooms-and-semiconductor-manufacturing-6634/</u>

<sup>&</sup>lt;sup>29</sup> <u>https://www.jedunn.com/projects/p127475-basebuildlayout-dependent</u>

# Figure 6: List of utility systems

Source: <u>Swagelock</u>

# Examples of Eligible Property

Eligible property under 48D for fabrication, ATP, and manufacturing equipment facilities could include, but is not limited to, the following:

- Photolithography tools

- Deposition and etching tools used in the processes of Chemical Vapor Deposition (CVD), Physical Vapor Deposition (PVD), and Damascene Electro Plating (DEP)

- E-Beam Operation tools (to repair masks), electroplating tools, and ion implant tools

- Mask manufacturing equipment

- Photomasks/reticles/pellicle, steppers, scanners and photoresist related equipment

- Emulation tools

- Inspection and metrology equipment, including scanning electron microscopes, atomic force microscopes, ion milling tools, optical inspection systems, wafer probes and optical scatterometer

- Rapid thermal processing tools (annealing tubes and vacuum ovens), melting laser annealing (MLA) equipment, wafer bonding equipment, physical removal processing tools (flycutter, DieSaw, and backgrind), and edge seal dispense

- Chemical mechanical polishing equipment

- Site preparation

- Construction/expansion/upgrade/modification of facility, including special construction to minimize vibrations and earthquake protection

- Site Infrastructure energy, water, natural gas, backup power generators, transformers, stormwater management, fire protection, other

- Sub fab

- Clean room equipment and specialty cleaning equipment

- Equipment and installation (wiped-film evaporators)

- Pumps and other tool specific abatement equipment and installation

- Chemical and gas delivery systems piping, storage and waste systems (including hazardous waste)

- Bulk chemical storage and purification systems (Liquid N2, Ar, H2, etc.)

- Semiconductor grade Water recycling and purification systems

- HVAC Air conditioning and air handling systems, critical cooling water systems, heating systems

- Ultra-pure water systems

- Specialized lighting

- Pollution controls air (abatement, scrubbers, stacks, etc.), wastewater treatment, waste systems

- Storage systems for critical inputs to the fabrication process (Masks, spare parts, front opening unified pods, etc.)

- Wafer stockers with temperature and air quality control

- Automated material handling system (AMHS) (wafer handling systems to move wafers within manufacturing facility)

- Advanced Wafer routing software systems and databases

- Manufacturing automation and control equipment, including mechanisms to move wafers among tools IT infrastructure

- Backup systems to ensure operational continuity

- Temperature control systems

- Locker/gowning rooms

- Security and/or monitoring systems/devices

- Warehousing and storage, and associated handling systems

- Failure analysis labs and equipment

- Quality assurance equipment including incoming goods, in-process inspection, and finished-good inspection

- Computer Data Center (CDC) and related facilities that is used for manufacturing monitoring, data analysis and related functions

- Software and IT programs that are used for manufacturing purpose;

- Jigs, hand tools, calibration equipment, temperature and pollution monitoring tools and etc. that are used in clean room;

- Transportation, trolleys and carts that are used to transport wafers

## 2. Assembly, Test, and Packaging Facilities

An IRS notice provides a high-level summary of ATP and its role in the manufacturing process:<sup>30</sup>

During the front-end process (wafer fabrication), silicon or other materials are prepared and wafers are fabricated and subjected to a number of processing steps to produce multiple copies of an electronic circuit or "die" on the wafer. This wafer fabrication is indisputably considered to be a manufacturing activity.

During the back-end process, after the die are separated and sorted, the following activities are conducted, which are generally known in the semiconductor industry as "assembly and test" activities (hereinafter "semiconductor assembly and test activities"). The good die are put through a series of processes to create the electrical connection(s) necessary for the device to function. Die are attached to a frame, substrate, printed-circuit board, or other material. The completed product is most commonly referred to as a "chip".

Outsourced semiconductor assembly and test (OSAT) vendors are the companies that offer integrated circuit (IC) packaging and test services, including wafer level services after fabrication and prior to separation of die, the separation of die and subsequent packaging and testing of separated die. OSATs provide package design support to fabless and non-fabless companies, packaging to silicon devices that are made by foundries, and test services prior to shipping to the customer. OSATs mainly focus on offering innovative packaging and test solutions for semiconductor companies in well-established markets such as communications, consumer & computing, automotive, aerospace, defense, and space in addition to emerging markets in industrial, medical, the Internet of Things (IoT), artificial intelligence (AI), and wearable devices. OSATs offer cost-effective and innovative packaging solutions that enable higher performance, processing speeds and functionality of ICs with a reduction in space in an electronic device.

OSAT companies come into major play at the end stage of the semiconductor manufacturing process after the wafer fabrication and wafer probe stages. OSATs offer packaging and assembly solutions that involve the processing of bare semiconductors into finished semiconductors, which helps in protecting the die as well as facilitating electrical connections and heat dissipation. After packaging the customer's die, OSATs conduct final testing to ensure that the packaged semiconductor meets performance specifications. OSATs offer a wide range of semiconductor test services that includes various types of final, system-level, wafer, and strip testing along with the complete end of line services up to and including final shipping.

<sup>&</sup>lt;sup>30</sup> See Internal Revenue Service Industry Directive, "Treatment of Semiconductor Assembly and Test Activities as Manufacturing" (March 16, 2006) (footnotes omitted), available at <u>https://www.irs.gov/businesses/treatment-of-</u> <u>semiconductor-assembly-and-test-activities-as-manufacturing</u>. See also *Building Resilient Supply Chains, Revitalizing American Manufacturing, and Fostering Broad-Based Growth: 100-Day Reviews under Executive Order 14017* (June 2021), *available at <u>https://www.whitehouse.gov/wp-content/uploads/2021/06/100-day-supply-chain-</u> <u>review-report.pdf</u> (hereinafter White House Report) at 41-43.*

Figure 7. Packaging and test services are an integral part of the worldwide semiconductor supply chain

# Source: Amkor Technology

# Figure 8. Test operations

Ship Source: <u>Amkor Technology</u>

Air Blow Area Class Air Blow Wafer Bumping Class 100 Upper Fab Assembly Class 1,000 3.4 m m nistan Bump <100 class Assembly & Test <1000 class Fab Total 12.9 m 4 m D.L.I Plenum (Sub Utility) 5.5 m Class 100 lenu

Figure 9. Example of an ATP clean room

Source: Amkor Technology

Figure 10. Example of an ATP facility

Source: Amkor Technology K5 Center of Excellence Facility in South, Korea

Figure 11. Example of an ATP clean room

Source: Amkor Technology

Figure 12. Example of fan-out flip chip attach equipment

Source: Amkor Technology

Figure 13. Component kitting

# Source: <u>Amkor Technology</u>

Figure 14. FCBGA & SiP thermal conductive bonding

# Source: Amkor Technology

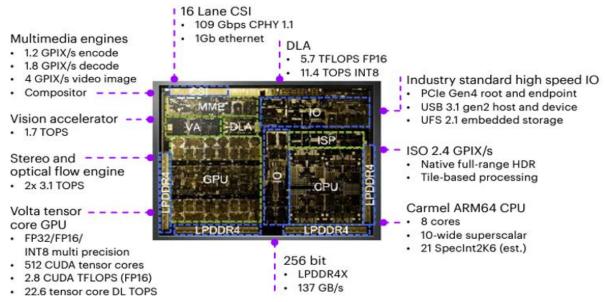

## 3. Chip Design

#### **Semiconductor Design**

Semiconductor design is an integral part of the chip fabrication process. The design stage requires large teams of highly skilled design engineers, each with different specialties, to prepare a design ready for production. Design companies collaborate closely with manufactures and ATP facilities to ensure their designs are successfully fabricated on a wafer and subsequently packaged in a device.

Semiconductor manufacturing is reliant on the key partnership between chip design and the fab, one cannot be done without the other. To illustrate the complexity of chip design, Figure 15 displays a diagram of a chip. Each part of the chip is carefully placed to ensure it provides the right processing power and energy efficiency. Design engineers work closely with the manufacturer to ensure the chip can be produced at the desired specification with the appropriate raw materials. For example, different semiconductor types require different materials to be produce for the desired product. Logic chips, commonly used in a computer processing unit (CPU), are produced on silicon wafers. Semiconductor power devices or radio frequency (RF) based chips, commonly used in applications that are exposed to very high temperatures, can be produced on sapphire wafers using Gallium Nitride (GaN).

#### Figure 15: Diagram of a sample chip

Source: Accenture

While many kinds of companies engage in semiconductor design, the major types are listed below:

- **Fabless companies.** (~47% of design-related value add) These companies focus exclusively on chip design, and partner with third-party merchant foundries to fabricate (that is, manufacture) their chips.

- Integrated device manufacturers (IDMs). (~51% of design-related value add) IDMs both design and manufacture chips. Within IDMs, design and manufacturing teams work together to bring to market new chips usually at in-house fabrication facilities.

- Original equipment manufacturers. (less than 2% of design-related value add) OEMs, like auto makers, use semiconductors as inputs for other products. Some OEMs have begun to design their own chips, primarily for their own products. For example, a cloud computing provider may design custom chips with specific features that execute specific tasks very well. OEMs are a growing presence in chip design and increasingly participate in the same product and talent markets as fabless companies or IDMs.

Another important part of the design ecosystem are electronic design automation (EDA) companies, which provide the design tools and reference flows and serve as trusted intermediaries between design companies and foundries. Third party IP providers design and license IP building blocks (processors, libraries, memories, interfaces, sensors and security).

Figure 16: Design life cycle

2

License IP cores from semiconductor IP houses

Integrate and harden IP cores from external vendors and in-house IP based on product requirements

Engage with EDA vendor for logical and physical design and floorplanning Leverage verification teams to ensure design is functional and manufacturable at designated fab Fab manufactures test wafer for final design validation

#### Source: <u>Accenture</u>

Fabless companies often work closely with a given foundry's design services team to ensure the compatibility of their designs with the foundry's fabrication processes. Close collaboration is critical, as scaling up new processes involves inherent uncertainties in modeling and reaching target manufacturing yields. Tangible property in respect to 48D could include, but is not limited to, the following:

- Facility construction/expansion/upgrade/modification

- Design automation tools

- Digital verification tools (simulation)

- Verification capital equipment (programmable hardware for circuit emulation)

- Test equipment

#### Semiconductor Manufacturing Equipment

Production of the equipment used in semiconductor manufacturing is equally capital intensive and requires skilled talent. Furthermore, the facilities that manufacture the equipment are complex and require similar support systems and structures as fabs. For example, these facilities contain clean rooms that require workers to wear protective gear to eliminate contaminants.

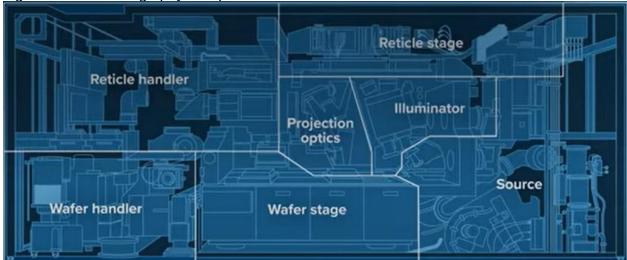

The White House supply chain report summarizes the manufacturing equipment used in the process of producing semiconductors as follows:

There are multiple categories of SME, each used in a different step of semiconductor production line. There are equipment types specific to manufacturing bare wafers (covered under "Materials" above), processing the bare wafer to semiconductors on a wafer (Front-end), packaging (Back-end), and equipment for manufacturing photomasks (mask manufacturing). Chip manufacturers need all the categories of front-end equipment in their manufacturing line. The cost of complex front-end semiconductor manufacturing equipment is a major reason (along with construction costs) for the high cost of a semiconductor fab. Front-end SME include equipment for fabrication steps, including lithography, etching, doping or ion implantation, deposition, and polishing or chemical mechanical planarization. Of particular note is metal organic chemical vapor deposition (MOCVD) equipment, a specific type of deposition equipment that deposits thin layers of certain metals, used primarily for the production of compound semiconductors, including those based on GaAs and GaN. Back-end SME includes equipment for ATP and advanced packaging.<sup>31</sup>